# DESIGN AND IMPLEMENTATION OF 4-BIT SHIFT REGISTER USING DOMINO AND DOIND LOGIC TECHNIQUES

Dr. S. Aruna<sup>1</sup>,B.Kiran Teja<sup>2</sup>, K. Srinivasa Naik<sup>3</sup> Assistant Professor<sup>1</sup>, M.Tech Scholar<sup>2</sup>, Associate Professor<sup>3</sup> <sup>1,2,3</sup>Department of Electronics and Communication Engineering <sup>1,2</sup>Andhra University College of Engineering, India <sup>3</sup>VIIT, India

**Abstract**: Dynamic CMOS logic circuits are utilised in the VLSI ICs to get the high performance of systems. But the parameter variations are serious problems in the deep sub-micron Technology by scaling down dimensions of transistors. Power consumption ,delay and leakage current are the performance parameters of any logic circuit. The performance of circuit reduces by the increment of power, delay and leakage current. To overcome these transistor parameter variations in nanometer technology design should be conscious of fluctuations.

In this DOIND logic design and domino logic design are used to study the variances issue. DOIND logic is designed from domino logic. DOIND logic design minimises leakage current as well as it minimises the variances issue with less delay disadvantage. Several processes, Voltages and Temperatures (PVT) variances studied at 60nm technology node for a domino logic and DOIND logic for Serial in Serial out (SISO) 4-BIT Shift Register, Parallel in Serial out (PISO) 4-BIT Shift Register and Parallel in Parallel out (PIPO) 4-BIT Shift Register, using Tanner EDA tool.

Keywords DOIND logic, Leakage current, PVT, nanometer Technology, domino, Scaling

# I. INTRODUCTION

Dynamic CMOS logic circuits are generally utilized in current computerized VLSI circuits on account of preeminent speed and size features of dynamic CMOS logic circuits as contrast with static CMOS logic circuits. Anyway dynamic CMOS logic circuits have less resistant to noise and expanded power dispersal than static CMOS logic circuits.

objective in the present VLSI circuit structures. So unique cooling hardware is important to eliminate more temperature delivered during the time of circuit operation. Power utilization in CMOS circuits can be dynamic or static. Dynamic power dissemination happens because of exchanging activities of short circuits current and charging and releasing load capacitances. Static power utilization is another sort of intensity dissemination in CMOS circuits. Discharge current flows with sub threshold source-to-drain discharge, reverse biased junction band-to-band burrowing, gate oxide burrowing, and other current drawn constantly from the power supply cause static power dissolution [7].

Today, the need of versatile frameworks and at the same time enhancement in battery execution delineates the power utilization is main consideration in CMOS VLSI circuits parameters [3]. To lessen dynamic power dissemination it is important to decrease the supply voltage of the circuit, decrease of supply voltage after a precise point influences the execution of the circuit, to keep up circuit execution of the circuit it is important to diminish the threshold voltage too, however it prompts leakage power dissolution. Leakage power can be lessened by expanding the threshold voltage [5].

## **II.RELATED WORK**

There are some methods to control inconstancy issue at transistor level structure. Body biasing is one of the method to relieve

fluctuation issue.

INDEP approach [3] is the method which has less impact of parameter variety in profound sub-micron region. This method has two additional embedded transistors between draw up and draw down systems which are input logic subordinate. Versatile body biasing is the method which reimburse impact of PVT fluctuations. For exactness and run time exchange off two calculations, process temperature versatile body inclination and process versatile body predisposition temperature versatile body inclination were proposed [4].

Sleep method [5] is the procedure for leakage control decrease. In the sleep method two sleep transistors (a PMOS and a NMOS) are included the circuit. The sleep transistor is switch on when circuit is dynamic mode and switch off when circuit is inactive mode[6] [7]. Ideal sleep vector is resolved for double Vth domino circuit under PVT changes [8].LECTOR-B system [9][10] is investigated under PVT varieties and has less impact parameter fluctuations

#### **III. PROPOSED LOGIC DESIGN**

In this paper Design of 4-Bit shift register using Domino logic and DOING logic are explained below. The operation of 4-Bit shift register in both the logic designs are discussed.

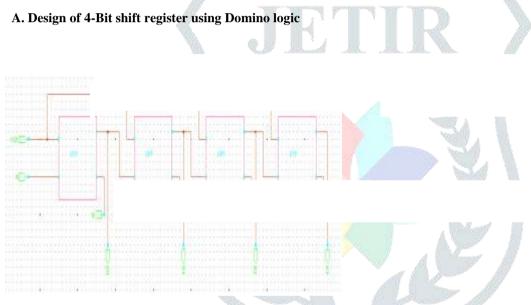

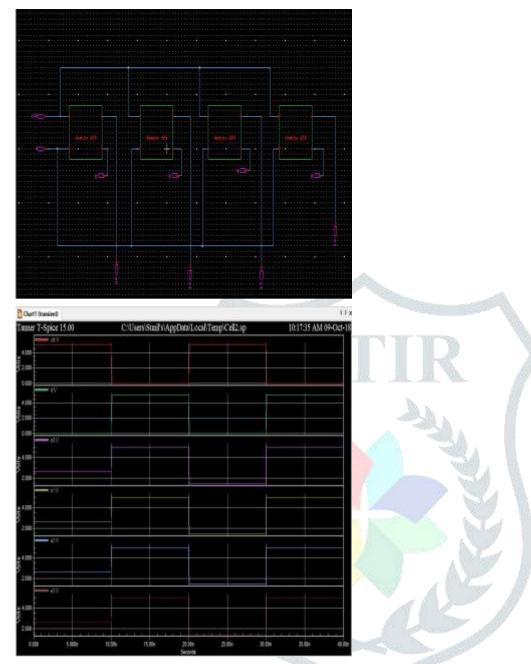

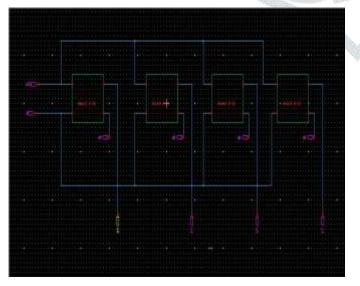

#### Fig 1.Domino logic 4-Bit Shift Register using Domino D-FF

Domino logic 4-Bit shift register using Domino D-FF is of serial input serial output type of shift register shown in fig 1.In this when clk signal is low, then d input should be 1 so that output s is 1.when the clk signal is high, then d input should be 0 so that output is 0.when both clk signal and input is same the output is undefined. n Bit-shift register designed using 'n' number of D-FFs. Each D-Latch designed using two 2-input nand gates followed by an inverter.

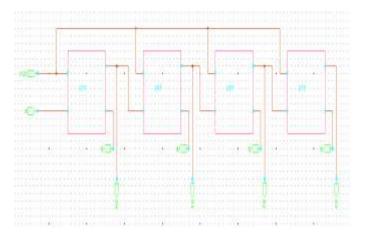

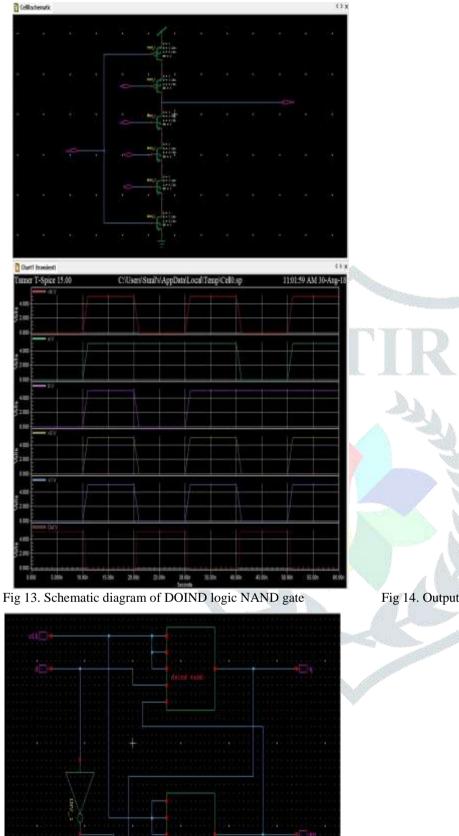

#### B. Design of 4-Bit shift register using DOIND logic

Fig 2.DOIND logic 4-Bit Shift Register using DOIND D-FF

DOIND logic 4-Bit shift register using DOIND D-FF is of serial input serial output type of shift register shown in fig 2. The Design and operation of DOING logic Design is in the same way as Domino logic design.

# **IV. SIMULATION RESULTS**

The TSPICE simulator is taken for the determination of power consumption, delay and leakage current of various types of 4-Bit shift registers. Here discussed about the Domino logic and DOIND logic serial in serial out (SISO) 4-Bit shift register, parallel in serial out (PISO) 4-Bit shift register and parallel in parallel out (PIPO) 4-Bit shift register.

C. Different types of Domino logic 4-Bit shift registers

Fig 3.Schematic diagram of Domino logic NAND gate

```

Fig 4. Output waveform of Domino logic NAND gate

```

|                               |            | Rented to the second               |

|-------------------------------|------------|------------------------------------|

|                               |            | 101100/1021001                     |

| In some and the source of the |            | E C                                |

|                               |            |                                    |

|                               |            | Randsteennest                      |

|                               |            | STILL CONTRACT                     |

|                               |            |                                    |

|                               |            |                                    |

|                               |            |                                    |

| ч.<br>9.8.                    |            |                                    |

|                               | 800008-000 | to the Party of the Local Distance |

|                               |            |                                    |

|                               |            | Ran (Aret Streth                   |

| mer T-Spice 15.00 | C3     | Users/Strifs/J | AppData/Locali | Temp/Cell.sp |        | 11:48:23 PM | 01-0ct-1 |

|-------------------|--------|----------------|----------------|--------------|--------|-------------|----------|

| 1000              |        |                |                |              |        |             |          |

| 1000              |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

|                   |        |                |                |              | -      |             |          |

| 1000              | _      |                |                |              | _      |             |          |

|                   |        |                |                |              |        |             |          |

| 1000              |        |                |                |              |        |             |          |

| EV                |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

| 1000              |        |                |                |              |        |             |          |

| 1000              |        |                |                |              |        |             |          |

| 1001              |        |                |                |              | _      |             |          |

| 100               |        |                |                |              | _      |             |          |

|                   |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

| 1000              |        |                |                |              | _      |             |          |

|                   |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

| 1.000             |        |                |                |              | _      |             |          |

| 21                |        |                | _              |              |        |             | _        |

| 1.000             |        |                |                |              |        |             |          |

| 100               |        |                |                |              |        |             |          |

| 1000              |        |                | _              |              |        |             |          |

| 1000              |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

|                   |        |                |                |              |        |             |          |

| 1001              | 11.00% | 15.304         | 30.00+         | nie          | 20.004 | 21.004      | 4010     |

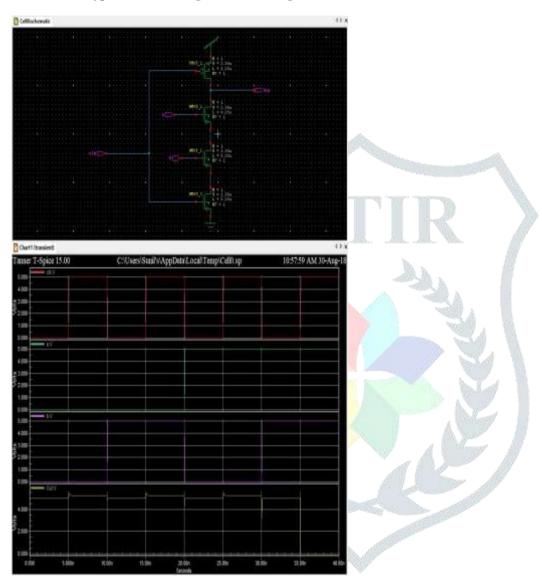

Fig 5. Schematic diagram of Domino logic D-Latch

Fig6. Output waveform of Domino logic D-Latch

Fig 9. Schematic diagram of Domino logic 4-Bit shift register (PISO)

Fig 10. Output waveform of Domino logic 4-Bit shift register (PISO)

Fig 11. Schematic diagram of Domino logic

4-Bit shift register (PIPO)

**D.Different types of DOIND logic 4-Bit shift registers**

Fig 12. Output waveform of Domino logic 4-Bit shift register (PIPO)

Fig 14. Output waveform of DOIND logic NAND gate

Fig 15. Schematic diagram of DOIND logic D-LATCH

Tener T-Spice 15.00 C:/Users/Sual's/AppDets/Local/Temp/CelL.sp 11:30:55 P94 01-Oct-18

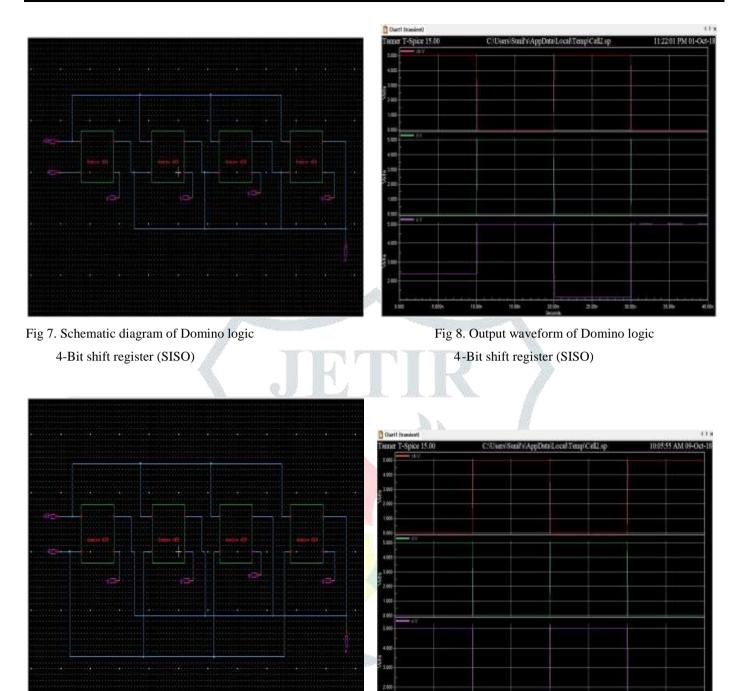

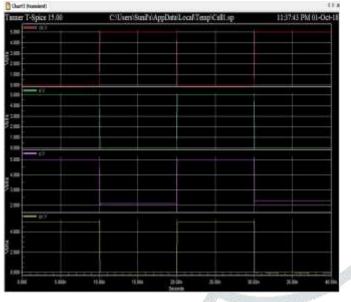

Fig 17. Schematic diagram of DOIND logic

Fig 16. Output waveform of DOIND logic D-LATCH

Fig 18. Output waveform of DOIND logic

4-Bit shift register (SISO)

4-Bit shift register (SISO)

|             |       | • •                 | •             | •        |          |                      |          |

|-------------|-------|---------------------|---------------|----------|----------|----------------------|----------|

| ati Basies0 |       |                     |               |          |          |                      |          |

|             | 1 Cil | ises(Surls)AppDut   | s:Local/Temp/ | Cel2.sp  | 10.30.11 | () ×<br>AM(09-Oct-18 |          |

|             |       | Sersi Seni s AppDon | a Local Tempi | Cell2.sp | 1030:18  |                      | IR       |

|             |       | Serv(StatTv AppDot  | a)Local/Temp/ | Cell sp  | 10.30-18 |                      | R<br>No. |

|             |       | SeeviStatTv AppDot  | sLecilTenp    |          | 103018   |                      | R        |

|             |       |                     | sLocilTempi   |          |          |                      |          |

2100

Fig 19. Schematic diagram of DOIND logic

15.89

4-Bit shift register (PISO)

10.004

1.00

Fig 20. Output waveform of DOIND logic 4-Bit shift register (PISO)

| er T-Spice 15.00 | Cillien/Smlv                           | AppData/Local? | Temp/Cell2.sp              |        | 10:37:34 AM | 05-Oct-1 |

|------------------|----------------------------------------|----------------|----------------------------|--------|-------------|----------|

| 1#V              |                                        |                |                            |        |             | 1        |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

| - ci             |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

| 4010             |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             | _        |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            | _      |             | _        |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             | _        |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             | _        |

|                  |                                        | - Vi           |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  |                                        |                |                            |        |             |          |

|                  | 1. 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                | And so the American Street |        | A           | 1.1.1    |

| 1000 -5.000H     | 15 00k 15 80k                          | 25.06          | 25 me                      | 36.000 | 35.00h      | 41.00    |

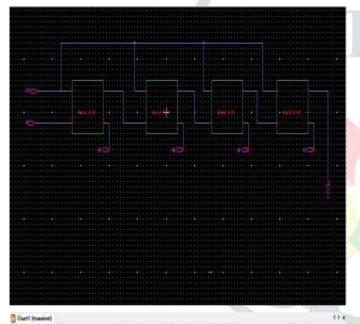

- Fig 21. Schematic diagram of DOIND logic 4-Bit shift register (PIPO)

- Fig 22. Output waveform of DOIND logic

- 4-Bit shift register (PIPO)

# E.Comparision of power, delay and leakage current for Domino and DOIND logic 4-Bit shift registers

|           |              | 16          |

|-----------|--------------|-------------|

| Parameter | Domino logic | DOIND logic |

| POWER     | 19.8876nW    | 11.5285Nw   |

| DELAY     | 10.0285nS    | 10.0113Ns   |

| LEAKAGE   | 1.40mA       | 1.285Ma     |

| CURRENT   |              |             |

Table 1. Comparision of power, delay and leakage current of Domino and DOIND 4-Bit shift registers

## VI .CONCLUSION

In this paper different types of 4-Bit shift registers are designed in Domino and DOIND logic designs. from the measurements of power, delay and leakage current DOIND logic gives good results compared to Domino logic. Variation in temperature from zero degrees to 120 degrees performance of DOIND logic far better than the Domino logic 4-Bit shift register.

## **REFERENCES:**

[1] M. Lanuzza, F. Frustaci, S. Perri and P. Corsonello, "Design of energy aware addercircuits considering random intra-die process variations," J Low Power Electron Appl, vol.1 no.1, 2011, pp. 97–108.

[2] D. Ghai, S.P. Mohanty, E. Kougianos and P. Patra, "A PVT aware accurate statistical logic library for high- k metal-gate nano-CMOS," IEEE int symp on quality electronic design (ISQED); 2009. pp. 47–54.

[3] V.K. Sharma, M. Pattanaik and B.Raj, "PVT variations aware low leakage INDEP approach for nanoscale CMOS circuit," Microelectronics reliability, vol. 54, 2014, pp. 90-99.

[4] S.V. Kumar, C.H. Kim and S.S. Sapatnekar, "Adaptive techniques for overcoming performance degradation due to aging in CMOS circuits," IEEE Trans VLSI System, vol. 19, no. 4, 2011, pp. 603–614.

[5] M. Powell, S.-H. Yang, B. Falsafi, K. Roy and T. N. Vijaykumar, "Gated-Vdd: A Circuit Technique to Reduce Leakage in Deepsubmicron Cache Memories," International Symposium on Low Power Electronics and Design, 2000, pp. 90-95.

[6] K.K. Kim and Y.B. Kim, "A novel adaptive design methodology for minimum leakage power considering PVT variations on nanoscale VLSI systems," IEEE Trans VLSI Syst, vol. 17, no. 4, 2009, pp.517–528.

[7] V. Neema, S.S.Chouhan, S. Tokekar, "Novel Circuit Technique for Reduction of Leakage Current in Series/Parallel PMOS/NMOS Transistors Stack", IETE Journal of Research, vol. 56, no. 6, 2010, pp. 350-354.

[8] N. Gong. J. Wang and R. Sridhar, "PVT Vatiations Aware Optimal Sleep Vector Determination of Dual Vt Domino OR Circuits", Proceedings of IEEE International Conference on SOC (SOCC 2011), 2011, pp. 359-364.

[9] A.P. Shah, V. Neema and S. Daulatabad, "Effect of Process, Voltage and Temperature (PVT) Variations in LECTOR-B technique at 70 nm technology node",

[10] A.P. Shah, V. Neema and S. Daulatabad, "Comparative study of Area, Delay and Power Dissipation for LECTOR and INDEP (Leakage control techniques) at 70 nm technology node", Proceedings of IEEE International Advance Computing Conference (IACC 2015), 2015, pp. 1-6.

[11] F. Moradi, A. Peiravi and H. Mahmoodi, "A New Leakage Tolerant Design for High Fan-in Domino circuits," Proceedings of The 16th International Conference on Microelectronics (ICM 2004), Dec 2004, pp. 493-496.

[12] M. H. Anis, M. W. Allam, and M. I. Elmasry, "Energy-efficient noise- tolerant dynamic styles for scaled-down CMOS and MTCMOS Technologies," IEEE Trans. Very Large Scale (VLSI) Syst., vol. 10, no. 2, April 2002, pp. 71–78.

[13] L. Ding, and P. Mazumder, "On Circuit technique to Improve Noise Immunity of CMOS Dynamic Logic," IEEE Trans VLSI System, vol. 12, no. 9, September 2004, pp. 910–925.

[14] H. Al-hertani, D. Al-Khalili and C. Rozon, "UDSM Subthreshold Leakage Model for NMOS Transistor Stacks," Microelectronics Journals, Vol 39, no. 12, 2008, pp. 1809-1816.

[15] B. S. Deepaksubramanyam and A. Nunez, "analysis of subthreshold leakage reduction in cmos digital circuits" Proceeding of 50th Midwest Symposium on Circuits and Systems (MWSCAS 2007), Aug. 2004, pp. 1400- 1404.